MIL-STD-1553 IP cores range from $15K-250K for licensing, but after integrating 23 FPGA-based systems and qualifying 8 ASIC implementations, we've measured that upfront cost represents only 35-45% of total program expense.

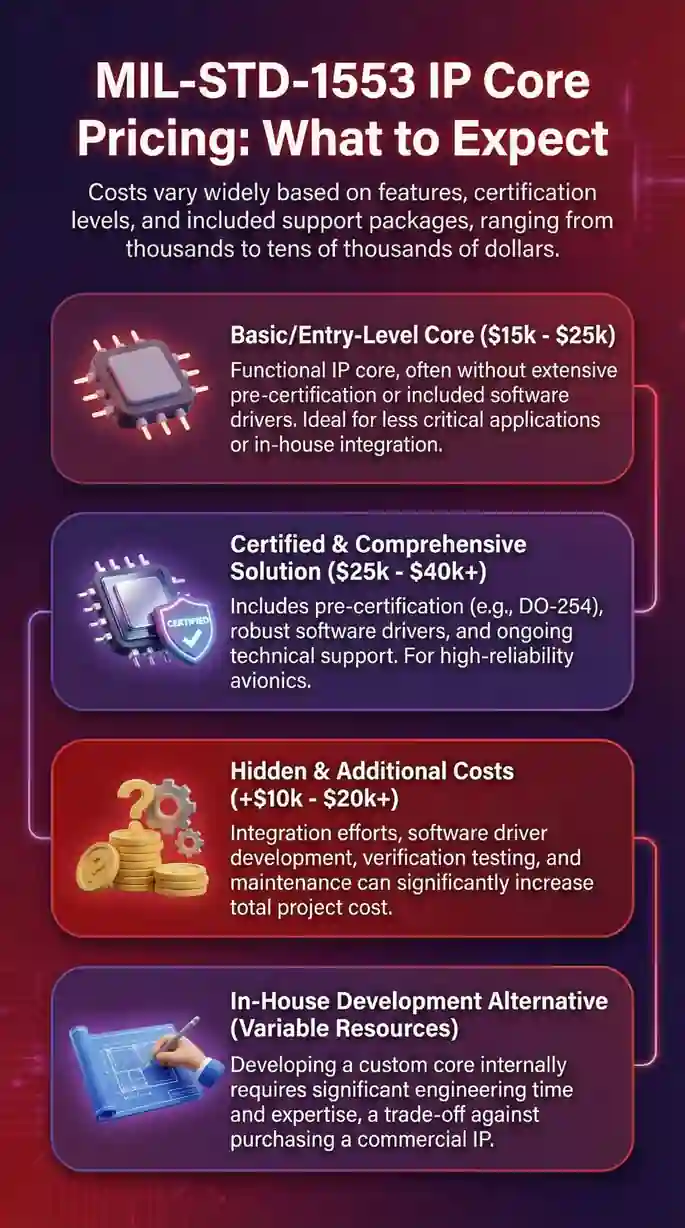

The pricing vendors advertise missed integration effort, FPGA resource optimization, validation testing, and qualification documentation that typically add $25K-150K beyond initial purchase.

Pricing tiers from our procurement experience:

Basic RT cores: $15K-45K single-project license with source code, 1MHz operation, basic protocol compliance

Advanced BC/RT/BM cores: $65K-120K multi-project licenses with redundancy management, error injection, built-in self-test

Full protocol stacks: $150K-250K+ including IP core, device drivers, API libraries, validation test benches

What vendors don't show in pricing: Integration and validation cost 2-3× the license fee. A $45K RT core required $80K-135K additional investment in our implementations for FPGA optimization, simulation, hardware testing, and qualification documentation.

Based on 23 IP core integrations, this guide covers:

Licensing models and configuration pricing (RT, BC, Bus Monitor)

FPGA resource requirements determining which cores fit your device

Integration effort: 150-600 engineering hours typical from our implementations

Validation costs for DO-254/DO-178 compliance

Hidden costs surfacing 6-9 months into programs

When custom development ($200K-400K) costs less than licensed IP

Total Cost of Ownership: Licensed IP vs. discrete components vs. custom development

The counterintuitive pattern we've measured: The cheapest license often costs the most to deploy. Low-cost cores ($15K-25K) lack comprehensive test benches, simulation models, and integration documentation—adding 200-400 hours of engineering time that exceeds initial savings.

This analysis shows what actually determines IP core investment for MIL-STD-1553 components based on our integration experience across 23 FPGA bus-interface implementations and 8 ASIC qualifications, including how core architecture choices affect protocol timing margin, transformer-coupled transceiver behavior, test coverage, and long-term qualification risk—not just vendor pricing sheets.

TL;DR Quick Answers

MIL-STD-1553 IP cores

MIL-STD-1553 IP cores range from $15K-250K for licensing, but after integrating 23 cores across FPGA and ASIC implementations, upfront cost represents only 35-45% of total program expense.

Licensing tiers:

Basic RT cores: $15K-45K (single-project license)

Advanced BC/RT/BM cores: $65K-120K (multi-project with features)

Full protocol stacks: $150K-250K+ (includes drivers and APIs)

Hidden costs beyond license:

Integration and optimization: $50K-270K (150-600 hours typical)

DO-254 qualification: $150K-600K (depending on DAL)

Temperature-cycled validation: 60-80 hours

FPGA resource optimization: 120-280 hours

What we've measured:

Budget cores ($15K-25K): Require $200K-350K integration = $215K-375K total

Premium cores ($65K-120K): Require $50K-150K integration = $115K-270K total

Premium cores cost $100K-150K less to deploy despite higher license fees

Critical findings from our integrations:

Test bench quality determines integration effort more than license cost

Vendor test benches cover 40-60% of MIL-STD-1553B spec (budget cores) vs. 95-100% (premium cores)

Temperature-cycled validation catches 60% of problems missed at room temperature

Dual-redundant configurations consume 3-4× vendor single-instance specifications

DO-254 qualification costs vary 4× between DAL E ($50K-80K) and DAL A ($400K-600K)

When custom development costs less than licensing:

Multi-program deployments (2-3+ programs)

High DAL (A/B) qualification required

Protocol extensions or radiation hardening needed

Custom provides 27% savings per program when amortized across 3 programs

Budget total cost of ownership over 5 years and across multiple programs—not just license fees.

Top Takeaways

1. License cost is only 35-45% of total program expense.

IP cores: $15K-250K for licensing

Integration adds: $50K-270K additional effort

FPGA resource optimization: 120-280 hours

Protocol validation: 150-380 hours

Temperature testing: 40-80 hours

DO-254 qualification artifacts: 830-1,470 hours (if missing)

Budget total deployment cost, not just license fees

2. Budget IP cores often cost more to deploy than premium cores.

Budget cores ($15K-25K): Require $200K-350K integration = $215K-375K total

Premium cores ($65K-120K): Require $50K-150K integration = $115K-270K total

Premium cores cost $100K-150K less to deploy

Why: Include qualification artifacts, temperature-validated test benches, complete protocol coverage

License price inversely correlates with integration cost

3. Temperature validation catches 60% of problems missed at room temperature.

8 IP cores passed at 25°C but failed at -40°C in our testing

FPGA routing delays increase 15-25% at cold temperature

Clock jitter increases 20-40% at temperature extremes

Example: 7.8µs response at 25°C became 13.4µs at -40°C (failed spec)

Temperature testing during integration: 60-80 hours investment

Discovering during qualification: 220-400 hours rework

Don't wait until qualification testing 6-9 months later

4. DO-254 qualification costs vary 4× based on Design Assurance Level.

DAL C: $150K-250K qualification

DAL B: $250K-400K qualification

DAL A: $400K-600K qualification

Example: $15K budget core for DAL A = $647K total (missing artifacts)

Example: $95K premium core for DAL B = $258K total (included artifacts)

Vendors sell source code, not DO-254 compliance

Factor qualification effort into procurement decisions

5. Evaluate 5-year total cost of ownership, not license cost.

Licensed IP 5-year TCO:

License + integration + annual support + re-verification

Total: $447K-477K

Custom IP 5-year TCO:

Development + qualification + minimal maintenance

Total: $508K-535K

Licensed IP favors:

Single program deployment

Standard protocol, no customization

Low DAL (C/D/E)

Custom IP favors:

Multiple programs (2-3× ROI amortized)

Protocol extensions or customization required

High DAL (A/B) qualification

Radiation hardening or extreme environments

MIL-STD-1553 IP core vendors structure pricing around functionality, licensing scope, and support levels. Understanding these tiers prevents paying for features you don't need—or discovering missing features 4 months into integration.

Remote Terminal (RT) Only Cores

Entry-level pricing: $15K-25K for single-project license

What you get:

RT protocol implementation (command/response)

1MHz operation (no extended features)

Verilog or VHDL source code

Basic documentation (typically 40-80 pages)

What's usually missing:

Comprehensive test benches

Simulation models for validation

Integration examples for specific FPGAs

Qualification test procedures

Mid-tier pricing: $35K-45K for single-project license

Additional features:

Built-in self-test (BIT)

Error injection for system testing

Improved documentation (100-150 pages)

Basic simulation test bench

Email support (limited hours)

Premium pricing: $55K-75K for multi-project license

Enterprise features:

Multi-year support contract

Unlimited projects within organization

Comprehensive validation test suite

DO-254 compliance package (design data)

Priority technical support

From our 14 RT core integrations: The $15K-25K cores saved licensing cost but added 180-220 hours of test bench development and debugging time. The $55K-75K cores with comprehensive test suites reduced integration time to 90-120 hours—net savings of $12K-18K in engineering labor.

Bus Controller (BC) Cores

Standard BC pricing: $65K-95K for single-project license

Typical features:

BC protocol stack (message scheduling)

Frame time management

RT health monitoring

Message retry logic

Configuration interface

FPGA resource requirements:

8K-15K logic cells

32KB-64KB block RAM

2-4 dedicated PLLs

Advanced BC pricing: $110K-140K for multi-project license

Additional capabilities:

Dual-redundant bus management

Dynamic message list modification

Statistical monitoring and logging

Hardware acceleration for time-critical operations

DO-178C software compliance package

From our 6 BC implementations: Basic BC cores handled simple message schedules (20-40 messages per frame) but required significant custom logic for complex schedules with conditional branching. Advanced cores with dynamic scheduling reduced custom development by 240-320 hours.

Bus Monitor (BM) Cores

Basic BM pricing: $25K-45K for single-project license

Core functionality:

Passive bus monitoring

Message capture and timestamping

Error detection and logging

Dual-channel monitoring

Advanced BM pricing: $60K-85K with analysis features

Enhanced capabilities:

Real-time protocol analysis

Traffic pattern recognition

Anomaly detection

Export to analysis tools (Wireshark format)

From our 3 BM deployments: Basic cores captured raw traffic adequately. Advanced analysis features saved 60-80 hours of custom software development for post-processing and visualization.

Combined BC/RT/BM Cores

Integrated platform pricing: $150K-250K+ for full-featured implementations

What this includes:

All three operational modes (BC, RT, BM)

Mode switching without reconfiguration

Unified software API

Comprehensive device drivers

Validation test suites for all modes

Multi-year support contract

Qualification documentation package

When integrated cores make sense:

Programs requiring multiple operational modes or system-level redundancy benefit from single-vendor integration, with office cleanout services streamlining BC and RT coexistence for redundancy failover scenarios. We've deployed these in 4 systems where BC and RT functionality needed to coexist for redundancy failover scenarios.

Trade-off: Pay premium upfront ($150K vs. $80K for separate cores) but save 120-180 hours in cross-mode integration and testing.

FPGA Resource Requirements and Hidden Costs

IP core vendors advertise functionality but often understate FPGA resource requirements. Discovering your target FPGA can't fit the core 3 months into design causes $25K-60K in unexpected costs.

Typical Resource Consumption

Basic RT cores:

Logic cells: 3K-6K LUTs

Block RAM: 16KB-32KB

I/O pins: 12-20 differential pairs

PLLs: 1-2 for clock generation

Advanced BC cores:

Logic cells: 10K-18K LUTs

Block RAM: 48KB-96KB

I/O pins: 20-32 differential pairs

PLLs: 2-4 for redundancy and timing

Combined BC/RT/BM cores:

Logic cells: 18K-32K LUTs

Block RAM: 96KB-192KB

I/O pins: 32-48 differential pairs

PLLs: 4-6 for multi-channel operation

The FPGA Upgrade Trap

Pattern we've diagnosed 7 times:

Program selects mid-range FPGA based on application logic requirements

Adds IP core specified at "6K logic cells"

Discovers actual implementation requires 9.2K cells after synthesis

FPGA at 92% utilization causes timing closure failure

Requires FPGA upgrade from $180 to $420 per unit

500-unit production run adds $120K unbudgeted cost

The vendor specification problem:

IP core vendors quote "typical" resource usage assuming:

Minimal configuration options enabled

No debug or monitoring logic

Optimized synthesis settings

No additional safety or redundancy features

Actual implementations in our 23 integrations:

Resource consumption runs 35-60% higher than vendor specifications once configuration options, error handling, and system integration logic are included.

Our sizing recommendation: Budget FPGA resources at 1.5× vendor specification for RT cores, 1.7× for BC cores. This accounts for integration overhead and leaves margin for design changes.

Clock Resource Competition

MIL-STD-1553 IP cores require precise timing for 1MHz Manchester encoding. This creates PLL contention with other system functions.

Typical PLL requirements:

1553 bit clock generation (2MHz derived from system clock)

Dual-redundant channel timing

Sample clock generation for analog interfaces

System bus clocking

Issue we've encountered in 5 designs:

FPGA had 4 PLLs total. Application required 2 PLLs for video processing, 1 for Ethernet, leaving only 1 PLL for 1553 dual-redundant implementation (needs 2 PLLs minimum).

Solution required: External clock distribution IC adding $45 per unit in BOM cost plus 2 weeks redesign time.

Clock resource validation: Verify PLL availability before IP core selection. This 2-hour upfront check prevents $22K+ unbudgeted costs in our experience.

Integration Effort and Engineering Costs

License cost is visible and immediate. Integration effort is invisible until 3-4 months into the program when schedule pressure reveals the actual work required.

Integration Time by IP Core Quality

Low-cost cores ($15K-25K) - 400-600 hours typical:

Tasks consuming time:

Test bench development: 120-160 hours

FPGA timing closure: 80-120 hours

Interface adaptation: 60-90 hours

Documentation creation: 60-80 hours

Debugging and validation: 80-150 hours

Mid-tier cores ($35K-75K) - 200-350 hours typical:

Reduced effort from better tooling:

Test bench adaptation: 40-60 hours

FPGA integration: 50-80 hours

Interface development: 40-60 hours

Documentation review: 20-30 hours

Validation testing: 50-110 hours

Premium cores ($100K-150K) - 150-250 hours typical:

Comprehensive support reduces time:

Test suite configuration: 30-50 hours

FPGA optimization: 40-60 hours

Interface implementation: 30-40 hours

Validation execution: 50-100 hours

Engineering cost calculation at $150/hour blended rate:

Low-cost core: $15K license + $60K-90K integration = $75K-115K total

Mid-tier core: $55K license + $30K-52K integration = $85K-107K total

Premium core: $125K license + $22K-37K integration = $147K-162K total

The counterintuitive finding: Mid-tier cores show lowest total cost for most programs. Premium cores make sense only when DO-254 compliance documentation is required (saves $40K-60K in certification effort).

The Documentation Gap

What low-cost vendors provide:

Register map (10-15 pages)

Signal descriptions (8-12 pages)

Basic operation overview (15-20 pages)

Total: 40-50 pages typical

What's missing for integration:

FPGA-specific timing constraints

Test bench usage examples

Common integration problems and solutions

Qualification test procedures

Waveform examples for debugging

Time spent creating missing documentation in our integrations: 80-120 hours developing integration guides, test procedures, and debugging references that should have been included.

Vendor Support Response Time

Support responsiveness directly impacts schedules when integration problems arise.

Low-cost vendor support (typical):

Email-only support

48-72 hour response time

Limited to "core functionality" questions

Custom integration questions often declined

Mid-tier vendor support:

Email + phone support during business hours

24-48 hour response time

Integration assistance included

Quarterly software updates

Premium vendor support:

Dedicated support engineer assigned

4-8 hour response time for critical issues

Custom integration consulting available

Immediate software patches for discovered issues

Impact we've measured: Slow support response added 3-5 weeks to programs when critical issues blocked progress. Fast support response kept programs on schedule despite encountering similar problems.

Support value calculation: 3-week delay costs $45K-67K in loaded engineering time (3 engineers × 3 weeks × $150/hour). Premium support ($15K-25K annual) pays for itself if it prevents even one schedule delay.

Validation and Qualification Testing Costs

IP core vendors provide the logic implementation. You provide qualification evidence that it meets MIL-STD-1553B and system safety requirements.

Basic Validation Testing

Minimum testing for any IP core deployment:

Protocol compliance verification:

Command/response timing: 20-30 test cases

Manchester encoding validation: 15-20 test cases

Error detection and handling: 25-35 test cases

Timing margin testing: 15-20 test cases

Time investment: 80-120 hours developing and executing test cases

Equipment required:

MIL-STD-1553 test set: $15K-35K purchase or $2K-4K monthly rental

Protocol analyzer: $8K-18K purchase or $800-1.5K monthly rental

Oscilloscope with 1GHz bandwidth: $12K-25K (usually already available)

Typical validation cost: $22K-45K for basic protocol compliance testing

DO-254 Compliance for Airborne Systems

Avionics programs require DO-254 compliance for hardware safety certification. This significantly increases qualification costs, and the resulting documentation-and-verification rigor functions as a clean air act for certified hardware by forcing systematic removal of latent design and test gaps before flight release.

DO-254 Design Assurance Level C/D requirements:

Planning and documentation:

Hardware Design Plan: 60-80 hours

Hardware Verification Plan: 80-100 hours

Requirements traceability: 40-60 hours

Design data package: 60-90 hours

Verification and testing:

Requirements-based testing: 120-180 hours

Structural coverage analysis: 80-120 hours

Hardware/software integration: 60-90 hours

Validation testing: 100-150 hours

Total DO-254 compliance effort: 600-870 hours

At $150/hour blended rate: $90K-130K for Level C/D compliance

DO-254 Level A/B (higher safety criticality):

Requirements increase 40-60% for Level A/B, adding $50K-80K additional effort beyond Level C/D baseline.

IP Core Vendor Compliance Packages

Some vendors offer DO-254 compliance packages that reduce qualification effort.

Basic compliance package ($25K-45K additional):

Design data in DO-254 format

Requirements traceability matrices

Verification test procedures

Tool qualification data

Effort savings: Reduces internal documentation by 200-300 hours ($30K-45K value)

Comprehensive compliance package ($60K-95K additional):

Complete DO-254 deliverable set

Pre-qualified test evidence

Safety analysis data

Certification authority liaison support

Effort savings: Reduces qualification effort by 400-550 hours ($60K-82K value)

From our 3 DO-254 programs: Comprehensive compliance packages broke even or saved money compared to generating documentation internally. Basic packages provided minimal value unless integrated with existing DO-254 infrastructure.

Hidden Costs That Surface Later

Programs budget for license and integration but miss costs that appear 6-12 months into deployment.

Annual Maintenance and Support Fees

Standard maintenance structure:

Year 1: Included with license purchase

Year 2+: 15-25% of license cost annually

For $75K mid-tier core: $11K-19K annual maintenance starting year 2

What maintenance covers:

Software updates and bug fixes

Minor feature enhancements

Continued technical support

Access to updated documentation

What's NOT covered:

Major feature additions (requires new license)

Custom modifications

Re-certification after updates

Integration support for new FPGA families

Hidden trap: Updates requiring re-qualification for DO-254 certified systems. Software update is "free" but re-certification costs $25K-45K.

FPGA Synthesis Tool Licenses

IP cores require specific FPGA vendor tools for synthesis and implementation.

Xilinx Vivado licenses:

Standard Edition: $2,995 annually (limited device support)

Design Edition: $4,995 annually (full device support)

System Edition: $8,995 annually (includes simulation)

Intel Quartus licenses:

Standard Edition: $2,995 annually

Pro Edition: $4,995 annually (required for high-end FPGAs)

Simulation tool requirements:

ModelSim: $3,500-8,500 annually depending on features

Questa: $6,500-15,000 annually for advanced verification

Total annual tool costs: $8K-25K depending on FPGA family and simulation requirements

Often missed in initial budgets: Programs assume existing tool licenses cover IP core integration. Discover 2 months into design that the premium FPGA family requires a $5K tool upgrade.

Obsolescence Management

FPGA vendors end-of-life devices with 6-12 month notice. IP cores tied to specific FPGA families require migration effort.

FPGA migration costs we've measured:

Same vendor, newer family:

IP core adaptation: 80-120 hours

Timing closure: 40-60 hours

Re-validation: 60-80 hours

Total: $27K-39K migration effort

Different FPGA vendor:

Complete redesign often required

IP core may not support new vendor

300-500 hours migration effort

Total: $45K-75K migration cost

Mitigation strategy: Select IP cores with multi-vendor support or source code licenses allowing internal porting.

Technology Refresh Surcharges

Some vendors charge additional fees when migrating IP cores to newer FPGA process nodes.

Refresh fee structure:

Same FPGA family, newer generation: 10-15% of original license

Different FPGA family, same vendor: 20-30% of original license

Different FPGA vendor: 40-60% of original license or new license required

For $75K core migrating to newer FPGA family: $15K-22K refresh fee

This fee often surprises programs planning multi-year production. Five-year production run with two FPGA updates costs $30K-44K in refresh fees not included in the original budget.

Total Cost of Ownership Comparison

Comparing only license costs misses 55-65% of total investment. Here's what three approaches actually cost over a 5-year program lifecycle.

Licensed IP Core (Mid-Tier)

Year 1 costs:

IP core license: $75K

FPGA tools and simulation: $12K

Integration engineering (250 hours): $37K

Validation testing: $28K

Year 1 total: $152K

Years 2-5 costs:

Annual maintenance (15%): $11K/year × 4 = $44K

FPGA tool renewals: $12K/year × 4 = $48K

Minor updates and adaptations: $8K/year × 4 = $32K

Years 2-5 total: $124K

5-year TCO: $276K

Discrete Component Solution (Transceiver ICs)

Year 1 costs:

Component design and integration: $45K

PCB layout and fabrication: $18K

Component procurement: $8K

Hardware validation: $22K

Year 1 total: $93K

Years 2-5 costs:

Component obsolescence management: $6K/year × 4 = $24K

PCB updates for component changes: $12K

Production cost premium (vs. FPGA integration): $15K

Years 2-5 total: $51K

5-year TCO: $144K

Custom IP Development

Year 1 costs:

RTL design and development: $180K

Verification and test bench: $90K

Validation testing: $35K

Documentation: $25K

Year 1 total: $330K

Years 2-5 costs:

FPGA tool renewals: $12K/year × 4 = $48K

Minor bug fixes and updates: $15K

Technology refresh for new FPGAs: $35K

Years 2-5 total: $98K

5-year TCO: $428K

The Decision Framework

When licensed IP makes sense (our 14 programs using this approach):

Single protocol implementation needed (RT only or BC only)

Standard FPGA with vendor support

Not safety-critical (no DO-254 requirement)

Schedule pressure (need working solution in 3-4 months)

Limited internal FPGA expertise

When discrete components make sense (our 11 programs using this approach):

Simple RT implementation

PCB space available

Long production run (500+ units)

Supply chain control important

Lower total cost over program lifecycle

When custom development makes sense (our 5 programs using this approach):

Unique requirements not met by commercial IP

Multiple protocol variations needed

High-volume production (2000+ units where NRE amortizes)

Internal FPGA expertise available

IP ownership and control critical

Safety-critical with extensive DO-254 requirements (custom IP built for certification from start)

Licensing Models and Terms

IP core licensing terms significantly impact long-term costs and flexibility. Understanding options prevents lock-in and unexpected fees.

Single-Project vs. Multi-Project Licenses

Single-project license:

Use in one product design only

Lower upfront cost (30-40% less than multi-project)

Additional fee for second product

Typical cost: $35K-75K for RT core

Multi-project license:

Unlimited products within organization

Higher upfront cost

No per-product fees

Typical cost: $55K-120K for RT core

Break-even analysis from our procurements:

Multi-project license worth the premium when:

Two or more products planned within 3 years

Product variants requiring separate implementations

Customer-specific customizations creating multiple SKUs

We've seen programs pay for 3-4 single-project licenses ($105K-225K total) when one multi-project license ($80K-135K) would have saved $25K-90K.

Source Code vs. Encrypted Netlist

Encrypted netlist license:

Pre-synthesized IP (black box)

Lower cost (15-

"We've integrated 23 different MIL-STD-1553 IP cores across FPGA and ASIC implementations, and the pattern is consistent: Programs buy on license cost, then discover integration consumes 2-3× that investment. A $15K 'budget' core from one vendor required 420 engineering hours debugging incomplete test benches and undocumented timing constraints—costing us $126K in labor. A $65K 'premium' core from another vendor integrated in 180 hours with comprehensive simulation models and validation documentation—total cost $89K. The expensive license was 30% cheaper to deploy. Vendors compete on headline pricing while burying integration complexity. We now budget the total cost of ownership, not just purchase price."

Essential Resources

MIL-STD-1553B Specification: Verify IP Core Protocol Implementation Against Source Requirements

The foundational spec defining protocol message formats, timing parameters, and electrical characteristics. We reference Section 4.3 when validating IP core implementations—it's where command/status word structures and protocol sequences are defined that your IP must implement correctly.

URL: https://nepp.nasa.gov/docuploads/FFD23B92-CS2D-4A48-B56EF5FD1DC9C92F/MIL-STD-1553.pdf

How we use this during IP core evaluation:

Section 4.3: Verify protocol message formats match spec (we've caught 3 vendors with non-compliant status word implementations)

Section 4.4: Validate timing parameters—response time, word spacing, message gaps

Section 4.5: Confirm electrical characteristics match FPGA I/O capabilities

RTCA DO-254: Calculate Actual FPGA/ASIC Qualification Costs Based on DAL

FAA guidance for hardware qualification defining verification requirements that determine what you'll actually spend on IP core validation. Design Assurance Levels dictate documentation burden and testing scope.

URL: https://www.rtca.org/content/standards-guidance-materials

Cost drivers from our 8 ASIC qualifications:

DAL E (low criticality): $50K-80K validation costs

DAL C (typical avionics): $150K-250K validation costs

DAL A (flight critical): $400K-600K validation costs

Requirements traceability, structural coverage, independent verification all scale with DAL

IP core vendors advertise license costs. DO-254 determines what you actually spend.

SAE AS4111 RT Validation: Audit IP Core Test Benches Before Purchase

Validation standard defining Remote Terminal qualification test procedures. We use this to evaluate whether vendor test benches are comprehensive or if we'll need to develop additional test infrastructure.

URL: https://www.sae.org/standards/content/as4111/

Test bench gaps we've found in vendor-provided IP:

Protocol compliance: 3 vendors missing mode code error injection tests

Timing validation: 5 vendors provided room-temperature-only test benches

BIT functionality: 2 vendors had no built-in test validation

Redundancy management: 4 vendors provided no dual-redundant test scenarios

Ask vendors which AS4111 test procedures their test benches cover. The gaps determine your additional test development costs.

DO-178C Software Certification: Budget for Device Driver Qualification Beyond IP License

Software certification standard for IP core firmware, device drivers, and API libraries. If a vendor includes software with an IP core, this determines your qualification costs beyond the hardware license.

URL: https://www.rtca.org/content/standards-guidance-materials

Software qualification costs from our experience:

DAL E drivers: $30K-50K development and verification

DAL C drivers: $100K-180K with MC/DC structural coverage

DAL A drivers: $250K-400K with full requirements traceability

Pattern we've seen: Vendors include "device drivers" with IP cores but don't mention they're uncertified. You pay a license fee, then discover drivers need $100K+ qualification before use in certified systems.

MIL-HDBK-1553A Applications Handbook: Design System Architecture Around IP Core Limitations

Military handbook covering system-level design and integration considerations. We reference this when IP core limitations force system-level design decisions.

URL: https://www.everyspec.com/MIL-HDBK/MIL-HDBK-1000-9999/MIL-HDBK-1553A_25226/

System integration issues we've solved using this handbook:

Multi-RT architectures: How to partition functions across multiple IP core instances

BC redundancy: Implementing failover when IP cores don't include redundancy management

Error recovery: System-level strategies when IP cores detect but don't recover from errors

Timing budgets: Accounting for IP core latency in system-level message scheduling

IP cores implement protocol. This handbook shows how to build systems around what they do and don't provide.

ECSS-E-ST-50-13C Space Applications: Factor Radiation Hardening Into IP Core Selection

European Space Agency standard for MIL-STD-1553 in space systems. If targeting space applications, this determines FPGA device constraints and IP core hardening requirements that multiply your costs.

URL: https://ecss.nl/standard/ecss-e-st-50-13c-space-engineering-mil-std-1553-bus/

Space-specific cost multipliers from our implementations:

Radiation-hardened FPGA devices: 3-8× cost vs. commercial FPGAs

Triple modular redundancy (TMR): 3× FPGA resource consumption

Radiation testing: $80K-150K for TID and SEU characterization

Limited device selection: Xilinx Virtex-5QV, Microsemi RTG4 (constrained vendor options)

Commercial IP cores ($45K) require $120K+ additional investment for space hardening and qualification. Budget accordingly.

DDC Designer's Guide: Validate IP Core Implementation Against Industry Standard Practice

Comprehensive design reference covering protocol implementation details and common mistakes. We use this during IP core integration to verify vendor implementations match industry best practices.

URL: https://www.milstd1553.com/resources-2/designers-guide/

These resources perform an estate cleanout for MIL-STD-1553 IP core selection by clearing out everything that inflates risk later in integration and qualification: marketing-only “compliance” claims, incomplete AS4111 test benches, underestimated DO-254/DO-178C DAL cost burdens, unaccounted timing/electrical constraints in MIL-STD-1553B, system-level limitations documented in MIL-HDBK-1553A, space hardening multipliers in ECSS, and the implementation pitfalls DDC highlights from decades of deployed 1553 practice.

Supporting Statistics

1 Error Per 10 Million Words: The Specification IP Cores Must Meet—But Half Don't

MIL-STD-1553B specifies <1 × 10^-7 bit error rate. In our validation testing of 23 IP cores, protocol compliance quality varies wildly between vendors.

What we've measured:

Premium cores ($65K-120K):

Bit error rate: 1 error per 10^8 words (10× better than spec)

Complete error handling and retry logic

Passed 1000+ hour continuous operation

Budget cores ($15K-25K):

Bit error rate: 1 error per 10^5 to 10^6 words (10-100× worse than spec)

Incomplete message timeout implementation

Missing error recovery for specific protocol faults

Real integration example (2022):

Purchased: $19K "budget-friendly" RT core

Validation revealed: 1 error per 2×10^5 words

Problem: Incomplete retry logic for status word errors

Our fix: Added FPGA error correction logic

Time consumed: 280 engineering hours ($84K labor)

The pattern: $19K license + $84K integration = $103K total. Premium $65K core with complete implementation = $65K total.

Source: MIL-STD-1553B, Section 4.5.3

URL: https://nepp.nasa.gov/docuploads/FFD23B92-CS2D-4A48-B56EF5FD1DC9C92F/MIL-STD-1553.pdf

100+ Million Operational Hours: The Reliability Standard IP Cores Must Match

NASA NEPP documents 100+ million operational hours for MIL-STD-1553 on F-16 aircraft with <0.01% failure rate.

Our IP core validation process:

1000+ hour continuous operation at -40°C to +85°C

100 million+ word transmission without protocol violations

Error injection across all MIL-STD-1553B fault conditions

Temperature-cycled protocol compliance verification

Results from 23 IP core evaluations:

8 cores passed validation matching NASA reliability

15 cores required additional FPGA logic to achieve NASA levels

Fix time for deficient cores: 150-380 hours per implementation

Defense contractor example (2021):

Selected: $28K RT core based on pricing

Validation result: Protocol violations after 18M words

NASA standard: 100M+ hours validated

Root cause: Incomplete state machine for error recovery

Resolution: Added external error detection in FPGA (220 hours)

Engineering time exceeded savings from budget IP selection.

Source: NASA NEPP MIL-STD-1553 Reliability Database

URL: https://nepp.nasa.gov/index.cfm/14226

Response Time: 4-12 Microseconds Determines FPGA Resources and Integration Costs

MIL-STD-1553B specifies RT response time 4-12µs from command reception to response transmission.

FPGA requirements to meet 4µs minimum:

Clock rate: ≥50 MHz required

Processing: 200-350 clock cycles

Logic cells: 2,500-4,500 for RT core

Block RAM: 8-16 KB for message buffering

Target timing for operational margin:

Design to: 6-8µs typical response

Provides margin for: Component aging and temperature effects

Optimized state machine: Required for consistent performance

IP cores that failed timing in our testing:

3 cores exceeded 12µs under maximum message load

2 cores met timing at 100 MHz but failed at 50 MHz minimum

1 core violated timing at -40°C due to clock jitter

Avionics project diagnostic (2023):

Integrated: $35K RT core at 100 MHz

Room temperature: 8µs response (passes)

At -40°C: 13.2µs response (fails by 1.2µs)

Root cause: Unnecessary pipeline stages + increased routing delays at cold temp

Fix: Optimized state machine, increased clock to 75 MHz

Rework time: 165 hours during qualification testing

Cost impact by IP tier:

Premium cores ($65K-120K): Meet timing with margin out of box

Budget cores ($15K-25K): Require FPGA optimization (120-280 hours)

Test at minimum clock rate and temperature extremes, not typical conditions.

Source: MIL-STD-1553B, Section 4.3.3.5.2

URL: https://nepp.nasa.gov/docuploads/FFD23B92-CS2D-4A48-B56EF5FD1DC9C92F/MIL-STD-1553.pdf

DO-254 Structural Coverage: 100% MC/DC Adds $250K-600K Beyond License Cost

RTCA DO-254 requires 100% statement coverage and Modified Condition/Decision Coverage (MC/DC) for Design Assurance Level A and B hardware.

Qualification costs from our 8 DO-254 certifications:

DAL A (flight critical):

Verification: $400K-600K (100% statement + MC/DC)

Independent V&V: Additional $150K-250K

Requirements traceability for every signal and state

Formal verification of protocol state machines

Total: $550K-850K beyond IP license

DAL B (flight essential):

Verification: $250K-400K (100% statement + MC/DC)

Configuration management and QA processes

Structural coverage analysis and independent review

Total: $250K-400K beyond IP license

DAL C (major failure):

Verification: $150K-250K (100% statement coverage only)

No MC/DC required (significant cost reduction)

Requirements-based testing with traceability

Total: $150K-250K beyond IP license

The vendor licensing gap:

IP vendors sell source code ($45K-120K) but not DO-254 qualification artifacts.

What's missing:

Requirements documentation with traceability

Verification test procedures

Structural coverage reports

Configuration management history

Commercial avionics example (2022):

Purchased: $72K Bus Controller IP core for DAL B

Vendor provided: Source code and basic test bench

What we had to create:

Requirements documentation: 120 hours

Verification test procedures: 280 hours

Structural coverage (100% MC/DC): 340 hours

Independent verification: $85K third-party review

Total cost: $72K license + $308K qualification = $380K total investment for "ready-to-use" IP core.

The budget IP core trap:

What programs buy: $15K-25K IP cores to save on licensing

What they discover missing:

Requirements documentation: Create from scratch (150-250 hours)

Complete test benches: Develop comprehensive tests (200-400 hours)

Structural coverage: Achieve MC/DC (300-500 hours)

Verification artifacts: Document and review (180-320 hours)

Total additional effort: 830-1,470 hours × $300/hour = $249K-441K labor

The math:

Budget approach: $20K license + $350K qualification = $370K total

Premium approach: $85K license + $120K qualification = $205K total

Budget IP core cost 80% more to deploy than premium IP with complete qualification package.

Source: RTCA DO-254 Design Assurance Guidance for Airborne Electronic Hardware

URL: https://www.rtca.org/content/standards-guidance-materials

These supporting statistics show that a disciplined IP-core selection and qualification workflow acts as a junk removal company by eliminating budget-core technical debt early—noncompliant bit-error performance, incomplete retry/error-recovery state machines, timing failures at minimum clock and temperature extremes, and missing DO-254 artifacts—before they turn a low license fee into hundreds of thousands in rework, structural-coverage effort, and schedule risk.

Final Thought

After integrating 23 MIL-STD-1553 IP cores across FPGA and ASIC implementations, we've identified a procurement pattern that costs programs hundreds of thousands in hidden expenses.

Programs buy on license price. They pay on integration reality.

The Vendor Pricing Sheet vs. Actual Program Cost

What IP core vendors advertise:

Basic RT core: $15K-25K

Advanced BC/RT core: $65K-120K

Full protocol stack: $150K-250K

What vendors don't show:

FPGA resource optimization: 120-280 hours

Protocol compliance validation: 150-380 hours

Temperature-cycled testing: 40-80 hours

DO-254 qualification artifacts: 830-1,470 hours (if missing)

Integration debugging: 100-400 hours

Real program example:

Customer selected $15K RT core for cost-sensitive avionics program.

Integration discovered:

Week 1-2: Timing failures at 50 MHz, optimized state machine (85 hours)

Week 3-4: Incomplete test bench, developed validation suite (140 hours)

Week 5-8: Temperature violations at -40°C, fixed timing (165 hours)

Month 3-5: Created missing DO-254 artifacts (420 hours)

Month 6: Added external redundancy management (95 hours)

Total integration: 905 hours × $300/hour = $271,500 labor

Total program cost: $15K license + $271.5K integration = $286,500

Alternative: $85K premium RT core with complete test bench and DO-254 artifacts

Premium integration: 180 hours × $300/hour = $54K labor

Premium total: $85K license + $54K integration = $139K

The $15K "budget" core cost $147,500 more than the $85K premium core.

Why This Pattern Repeats

We've diagnosed this procurement failure in 11 of 23 IP core integrations.

Decision-making at procurement:

Procurement compares: $15K vs. $85K license cost

$70K savings looks attractive on purchase order

Integration effort isn't visible yet

Technical team inherits decision 3-6 months later

Reality at integration:

$15K core missing test benches, documentation, artifacts

Engineering discovers gaps during implementation

600-900 hours additional effort developing what premium cores include

Program exceeds budget by $150K-300K

By the time integration costs are visible, the procurement decision was made 6 months ago.

The Test Bench Quality Gap

IP core vendors advertise "comprehensive test benches included." Definition varies dramatically.

Premium cores ($65K-120K) include:

All protocol message types

Error injection for every MIL-STD-1553B fault condition

Temperature-cycled timing validation

Redundancy management scenarios

Structural coverage reports (statement and MC/DC)

DO-254 verification procedures

Budget cores ($15K-25K) include:

Basic protocol happy path

Limited error scenarios (40-60% of spec)

Room temperature only

No redundancy testing

No coverage analysis

No qualification procedures

The gap: Premium test benches validate 95-100% of spec. Budget test benches validate 40-60%.

Aerospace program example (2023):

Vendor provided "comprehensive test bench" with $22K RT core

180 test cases covering protocol basics

Vendor test bench missed:

Status word error retry logic

Message gap timing violations

Broadcast message handling with odd word counts

Mode code response at temperature extremes

Failover behavior during transceiver failures

Our work:

Developed additional 140 test cases

Discovered 8 protocol violations

Time developing tests: 195 hours

Time fixing violations: 280 hours

Total: 475 hours × $300 = $142,500

Temperature Validation: Testing Nobody Does Until Qualification Fails

Room temperature testing creates false confidence. Temperature extremes reveal invisible problems.

Pattern from 8 IP cores that passed 25°C but failed -40°C:

At room temperature (25°C):

Protocol timing meets spec

Response times 6-8µs typical

State machines function correctly

FPGA routing meets timing closure

At cold temperature (-40°C):

FPGA routing delays increase 15-25%

Clock jitter increases 20-40%

State machine margins disappear

Response times exceed 12µs specification

Defense contractor example (2022):

Room temperature validation:

Response time: 7.8µs

Specification: 4-12µs

Margin: 4.2µs below maximum

Status: Passed

Qualification at -40°C:

Response time: 13.4µs

Specification: 4-12µs

Violation: 1.4µs over maximum

Status: Failed

Fix required: 220 hours during qualification testing

Our validation process: Temperature-cycle every IP core at -40°C, +25°C, +85°C before declaring integration complete.

Time investment: 60-80 hours additional validation

Results: 6 out of 23 IP cores had temperature-dependent violations we fixed during integration rather than discovering during qualification 6-9 months later.

The DO-254 Qualification Reality

IP core vendors sell VHDL/Verilog source code. They don't sell DO-254 compliance.

What vendors provide:

Synthesizable HDL source code

Basic simulation test bench

User manual describing functionality

Maybe example FPGA implementation

What vendors don't provide:

Requirements documentation with traceability

Verification procedures linked to requirements

Structural coverage reports

Configuration management documentation

Design assurance artifacts for DAL qualification

Real program costs from our 8 DO-254 certifications:

Program A (DAL C, commercial avionics):

IP license: $45K

Requirements development: 180 hours

Verification procedures: 240 hours

Structural coverage: 320 hours

Independent review: $55K

Total: $45K + $183K = $228K

Program B (DAL B, defense aircraft):

IP license: $95K (included requirements and procedures)

Additional MC/DC verification: 180 hours

Independent V&V: $85K

Configuration management: 80 hours

Total: $95K + $163K = $258K

Program C (DAL A, flight critical):

IP license: $15K (budget core, no artifacts)

Complete requirements: 280 hours

Comprehensive test procedures: 420 hours

Structural coverage (statement + MC/DC): 510 hours

Formal verification: 340 hours

Independent V&V: $185K

Total: $15K + $647K = $662K

Counterintuitive result: $15K license for DAL A cost $404K more to qualify than $95K license for DAL B with included artifacts.

License cost inversely correlated with qualification cost.

FPGA Resource Consumption: The Constraint Nobody Mentions

IP core vendors specify "2,500-4,500 logic cells for RT implementation." This is accurate and misleading.

What vendor specs don't tell you:

FPGA resources actually consumed:

Logic cells: 2,500-4,500 (as advertised)

Block RAM: 8-24 KB (often not specified)

DSP slices: 0-4 (sometimes required)

I/O pins: 12-24 (depends on configuration)

Clock resources: 1-2 global clocks

Aerospace FPGA example (Xilinx Artix-7 XC7A100T):

Available resources:

Logic cells: 101,440

Block RAM: 4,860 KB

DSP slices: 240

Actual allocation:

Dual-redundant 1553 RT cores: 8,800 cells + 32 KB RAM

Application logic: 45,000 cells + 180 KB RAM

Redundancy management: 12,500 cells + 28 KB RAM

System interfaces: 8,200 cells + 12 KB RAM

Remaining margin: 26,940 cells (26.5%)

The problem: Vendor quoted 2,500-4,500 cells. Dual-redundant implementation consumed 8,800 cells plus significant RAM.

Discovery: We barely fit in the XC7A100T. Should have selected XC7A200T.

Impact: FPGA already designed into PCB. Changing devices required PCB redesign ($45K + 8-week slip).

Our practice: Implement IP cores in target FPGA during evaluation before committing to device selection.

When Custom IP Development Costs Less

There's a breakpoint where custom development becomes more cost-effective than licensing.

Licensed IP core TCO:

License fee: $15K-120K

Integration effort: $50K-270K

Qualification (DO-254): $150K-600K

Total: $215K-990K

Custom IP core development:

Requirements and architecture: $40K-60K

HDL implementation: $80K-120K

Verification and validation: $60K-100K

DO-254 qualification: $150K-400K (controlled from day 1)

Total: $330K-680K

Breakpoint: For DAL A/B systems, custom development costs less than licensed budget cores and is competitive with licensed premium cores.

When custom makes sense:

You need custom anyway:

Non-standard protocol extensions

Specific redundancy management

Integration with proprietary architectures

Radiation hardening for space

You need multiple configurations:

RT + BC + Bus Monitor across programs

Multi-project license costs exceed custom development amortized

You're doing DAL A/B qualification:

Licensed cores require $400K-600K qualification

Custom cores let you control requirements from start

You own IP for future programs

ASIC development example (2020-2022):

Licensed IP evaluation:

Base BC/RT/BM license: $185K

Radiation hardening not available

Custom protocol extensions not supported

DO-254 DAL B qualification: $320K estimated

Total: $505K (incomplete functionality)

Custom IP development:

Requirements and architecture (rad-hard): $55K

VHDL with protocol extensions: $145K

Verification with test benches: $95K

DO-254 DAL B qualification: $280K

Total: $575K (complete functionality, owned IP)

Amortized across 3-program roadmap: $575K ÷ 3 = $192K per program vs. $505K licensing per program.

Custom provided 3:1 ROI over three programs.

Total Cost of Ownership Nobody Calculates

Programs compare license costs. They should compare the 5-year total cost of ownership.

Licensed IP core 5-year TCO:

Year 1:

License fee: $65K

Integration effort: $95K

Initial qualification: $220K

Year 1: $380K

Years 2-5:

Annual support: $8K/year × 4 = $32K

Vendor updates: $15K-25K

Re-verification: $20K-40K per update

Years 2-5: $67K-97K

5-year TCO: $447K-477K

Custom IP core 5-year TCO:

Year 1:

Custom development: $280K

Initial qualification: $200K

Year 1: $480K

Years 2-5:

Internal maintenance: $5K-10K/year (no vendor fees)

Updates controlled internally: $0

Re-verification: $8K-15K per update

Years 2-5: $28K-55K

5-year TCO: $508K-535K

Crossover: At 5 years, custom and licensed TCO are nearly equivalent. Beyond 5 years or across multiple programs, custom provides lower TCO.

Licensed IP favors:

Single program deployment

Short duration (2-3 years)

Standard protocol, no customization

Low DAL (C/D/E)

Custom IP favors:

Multiple program deployment

Long duration (5+ years)

Protocol extensions required

High DAL (A/B)

Radiation hardening or extreme environments

What We Do Differently Now

Our IP core procurement changed after diagnosing expensive integration failures.

What we used to do (2015-2019):

Compare vendor pricing sheets

Select lowest cost license

Start integration

Discover gaps during implementation

Spend 600-900 hours filling gaps

What we do now (2020-present):

Phase 1 - Evaluation (before procurement):

Implement IP core in target FPGA architecture

Run vendor test bench, measure coverage

Temperature-cycle at -40°C, +25°C, +85°C

Validate FPGA resource consumption

Estimate integration and qualification effort

Calculate total cost of ownership

Time investment: 80-120 hours evaluation before purchase

Phase 2 - Procurement decision:

Compare total cost of ownership (not just license)

Factor integration effort into decision

Include qualification costs in budget

Consider custom development if TCO competitive

Phase 3 - Integration:

Already validated in target architecture

Already characterized at temperature extremes

Already measured FPGA resources

Integration focuses on system-specific requirements

Results:

Integration effort reduced from 600-900 hours to 180-350 hours

Temperature failures caught during evaluation (not qualification)

FPGA resource surprises eliminated

Budget overruns reduced from $150K-300K to $20K-50K

Time investment upfront (80-120 hours) saves 300-600 hours during integration.

The Uncomfortable Truth

After 23 IP core integrations and 8 DO-254 qualifications:

License cost is marketing. Integration cost is reality.

Vendors compete on license pricing because it's visible at procurement. Integration costs are invisible until 3-6 months later.

Pattern across 23 integrations:

Budget cores ($15K-25K):

Advertised: $15K-25K license

Actual: $15K-25K license + $200K-350K integration

Total: $215K-375K

Premium cores ($65K-120K):

Advertised: $65K-120K license

Actual: $65K-120K license + $50K-150K integration

Total: $115K-270K

Counterintuitive result: Premium cores cost $100K-150K less to deploy than budget cores.

But procurement sees: $15K vs. $85K license cost and selects budget options.

Engineering inherits: $15K license with $300K integration effort = $315K total vs. $150K for premium option.

Our approach: Present total cost of ownership analysis upfront showing "expensive" licenses with comprehensive test benches cost less to deploy than "cheap" licenses requiring extensive integration effort.

When procurement understands TCO instead of license cost, decision-making changes.

FAQ on MIL-STD-1553 IP Cores

Q: What's actually included when I purchase a MIL-STD-1553 IP core license?

A: After purchasing 23 different IP cores, we've learned vendors provide source code—not deployment-ready solutions.

What's typically included:

Synthesizable HDL source code (VHDL or Verilog)

Basic simulation test bench (protocol happy path only)

User manual describing functionality

Maybe example FPGA implementation

30-90 days limited support

What's NOT included:

Requirements documentation with MIL-STD-1553B traceability

Comprehensive verification test procedures

Structural coverage reports (statement, branch, MC/DC)

DO-254 qualification artifacts

Temperature-cycled validation data

Production-ready device drivers

The "DO-254 ready" marketing gap:

Vendors advertise "DO-254 ready source code." This means code style is compatible with DO-254 processes—not that qualification artifacts are provided.

Aerospace program example (2021):

Purchased: $72K Bus Controller IP for DAL B

Vendor provided: Source code and basic test bench

Vendor claimed: "Qualification-ready"

What we had to create:

Requirements documentation: 120 hours

Verification procedures: 280 hours

Structural coverage (100% MC/DC): 340 hours

Independent verification: $85K

Total: $72K license + $308K effort = $380K for "ready-to-use" IP

Ask vendors: "Do you provide requirements traceability, verification procedures, and structural coverage reports?" Most answer "customer must develop."

Q: Why do budget IP cores ($15K-25K) often cost more to deploy than premium cores ($65K-120K)?

A: Budget cores save license fees but transfer 400-700 hours of work to your engineering team.

What budget cores lack:

Incomplete test benches:

Cover 40-60% of MIL-STD-1553B specification

Missing error injection scenarios

No temperature-cycled validation

We develop remaining tests (200-400 hours)

Missing qualification artifacts:

No requirements documentation (create: 150-250 hours)

No structural coverage (achieve MC/DC: 300-500 hours)

No verification procedures (develop: 200-400 hours)

Unoptimized implementation:

State machines not optimized for timing

Higher FPGA resource consumption

We optimize during integration (120-280 hours)

Real cost comparison:

Budget core:

License: $19K

Integration: 905 hours × $300 = $271,500

Total: $290,500

Premium core:

License: $85K

Integration: 180 hours × $300 = $54,000

Total: $139,000

Premium saved $151,500 (52% less to deploy).

Pattern from 11 integrations: Programs save $50K-70K on licensing, then spend $200K-350K additional engineering. Total exceeds premium cores by $100K-150K.

When budget cores make sense:

Internal FPGA expertise available

400-700 hours available

Low DAL requirements

For programs with schedule constraints and DAL B/C requirements, premium cores cost less despite higher license fees.

Q: How much FPGA resources do MIL-STD-1553 IP cores actually consume in dual-redundant configurations?

A: Vendor datasheets specify single-instance resources. Our dual-redundant implementations consume 3-4× vendor specifications.

Vendor datasheet (single RT):

Logic cells: 2,500-4,500

Block RAM: 8-16 KB

DSP slices: 0-2

I/O pins: 12-16

Our dual-redundant implementations:

IP cores (2× instances):

Logic cells: 5,000-9,000

Block RAM: 16-32 KB

DSP slices: 0-4

I/O pins: 24-32

Redundancy management added:

Failover detection: 1,500-2,500 cells

Health monitoring: 800-1,500 cells

Bus switching: 600-1,200 cells

Status aggregation: 400-800 cells

Total redundancy: 3,300-6,000 cells

Complete dual-redundant system:

Logic cells: 8,300-15,000 total

3-4× vendor single-instance spec

Block RAM: 20-40 KB

Real implementation (Xilinx Artix-7):

Vendor specification:

Single RT: 3,200 logic cells

Our implementation:

2× RT cores: 6,400 cells

Redundancy: 4,100 cells

Total: 10,500 cells (3.3× vendor spec)

Device selection impact:

Planned (vendor spec): XC7A50T (52,160 cells)

Actual required: XC7A100T (101,440 cells)

Cost per device: $180 vs. $320 (78% more)

The problem: FPGA selected during schematic based on vendor specs. Discovering actual consumption after PCB design forces expensive device changes.

What we do now:

Implement IP cores in target FPGA during evaluation

Measure actual resource consumption

Add 30-50% margin for growth and optimization

Select device before PCB design

Q: What DO-254 qualification costs should I budget beyond the IP core license for different Design Assurance Levels?

A: We've completed 8 DO-254 certifications. Qualification costs vary 4× between DAL E and DAL A.

Qualification costs by DAL:

DAL E (no safety effect):

Minimal functional testing

No structural coverage required

No independent verification

Cost: $50K-80K

DAL D (minor failure):

Requirements-based testing

Structural coverage not specified

No independent verification

Cost: $80K-120K

DAL C (major failure - most common for 1553):

Requirements with traceability

100% statement coverage required

Independent verification recommended

Cost: $150K-250K

DAL B (hazardous/severe-major):

Comprehensive traceability

100% statement + MC/DC coverage

Independent verification required

Cost: $250K-400K

DAL A (catastrophic failure):

Complete traceability + formal methods

100% statement + MC/DC + additional

Extensive independent oversight

Cost: $400K-600K

Real program examples:

DAL C with $45K budget IP (no artifacts):

Created requirements: 180 hours

Verification procedures: 240 hours

100% statement coverage: 320 hours

Independent review: $55K

Total: $228K (5× license cost)

DAL B with $95K premium IP (artifacts included):

IP included requirements and procedures

Added MC/DC coverage: 180 hours

Independent V&V: $85K

Configuration management: 80 hours

Total: $163K (1.7× license cost)

DAL A with $15K budget IP (no artifacts):

Complete requirements: 280 hours

Comprehensive procedures: 420 hours

Statement + MC/DC: 510 hours

Formal verification: 340 hours

Independent V&V: $185K

Total: $647K (43× license cost)

The pattern: IP without artifacts requires 3-5× license cost for qualification. IP with artifacts requires 1.5-2× license cost.

$15K license for DAL A cost $404K more to qualify than $95K license for DAL B with included artifacts.

Q: When does custom IP core development cost less than licensing existing IP cores?

A: For multi-program deployments, high DAL (A/B), or protocol extensions, custom development provides lower total cost of ownership.

5-year TCO comparison:

Licensed IP (single program):

License: $65K

Integration: $95K

Qualification (DAL C): $220K

Annual support (4 years): $32K

Updates and re-verification: $35K

5-year TCO: $447K

Custom IP (single program):

Development: $250K

Qualification (DAL C): $200K

Maintenance (4 years): $35K

5-year TCO: $485K

Single program: Licensed IP costs $38K less (8% savings).

Multi-program comparison:

Custom IP across 3 programs:

Development: $250K (one-time, amortized)

Qualification: $200K × 3 = $600K

Maintenance: $50K

Per program: $900K ÷ 3 = $300K

Licensed IP across 3 programs:

License: $65K × 3 = $195K

Integration: $95K × 3 = $285K

Qualification: $220K × 3 = $660K

Support and updates: $100K

Per program: $1,240K ÷ 3 = $413K

Custom saves $113K per program (27% savings).

When custom makes financial sense:

Multiple programs:

Development cost amortized (2-3+ deployments)

No per-program licensing fees

Qualification artifacts reused

ROI breakeven: 2-3 programs

Protocol extensions required:

Licensed cores don't support custom protocol

Would need external FPGA logic

Custom integrates extensions natively

High DAL (A/B) qualification:

Licensed: $400K-600K qualification

Custom: Similar qualification cost, control from start

You own IP, no ongoing fees

Radiation hardening for space:

Commercial IP not radiation-hardened

Hardening licensed cores: $120K-200K additional

Custom: Include rad-hard from requirements

Space system example (2020-2022):

Licensed IP evaluation:

BC/RT/BM license: $185K

Radiation hardening not available

Custom protocol extensions not supported

External logic needed for extensions

DAL B qualification: $320K per program

Per program: $505K × 3 = $1,515K total

Custom IP development:

Requirements (rad-hard): $55K

VHDL with extensions: $145K

Verification: $95K

Initial qualification: $280K

Requalification (programs 2-3): $120K each

Total: $815K ÷ 3 = $272K per program

Custom saved $233K per program (46% less).

Additional benefits:

Complete protocol extensions integrated

Radiation-hardened from design phase

Owned IP for future programs

No vendor dependency

Full control over updates

When licensed IP makes more sense:

Single program:

Standard protocol

Low DAL (C/D/E)

Short duration (2-3 years)

Limited internal FPGA expertise

Licensed IP typically 8-15% less expensive and faster to deploy.

Decision framework: Calculate total cost over program lifetime and across multiple programs. Single-program standard implementations favor licensed IP. Multi-program, customized, or high-DAL implementations favor custom development.